Xilinx偺FPGA偱DDS傪偮偔傠偆

Xilinx偺FPGA偱DDS傪偮偔傠偆

FPGA偱梀傇丅

*夞楬恾偼偦偺偆偪偄傟傑偡丅

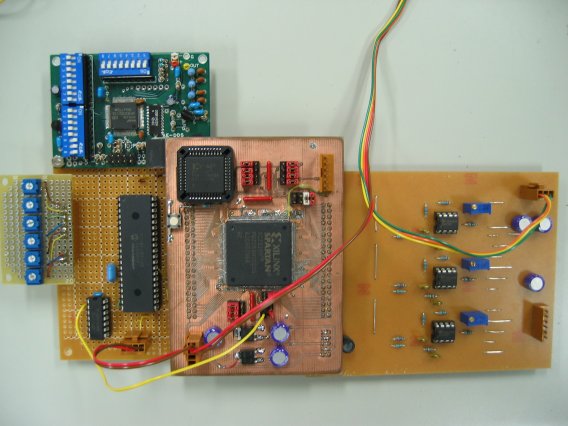

偁傞恖偺埶棅偱俁憡偺僒僀儞攇傪埵憡曄壔丄怳暆曄壔丄廃攇悢曄壔偱偒傞憰抲傪嶌偭偰傎偟偄偲偄偆偙偲偩偭偨偺偱憗懍傗偭偰傒傑偟偨丅偙傟偼偙偺偲偒偺惂嶌婰偱偡丅

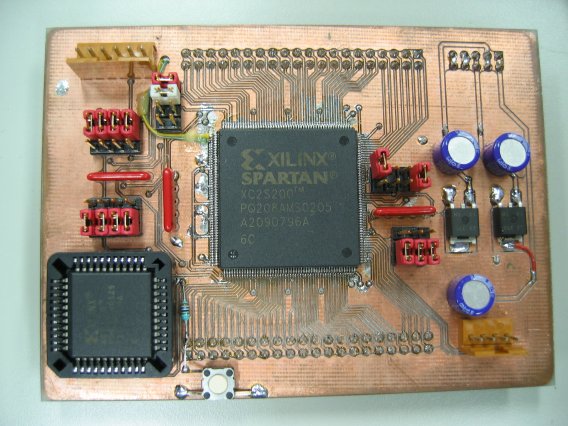

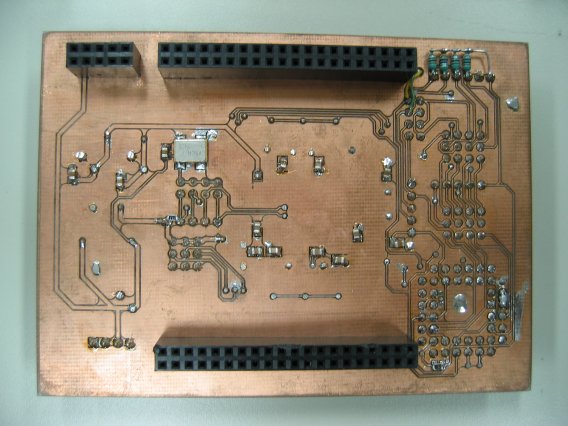

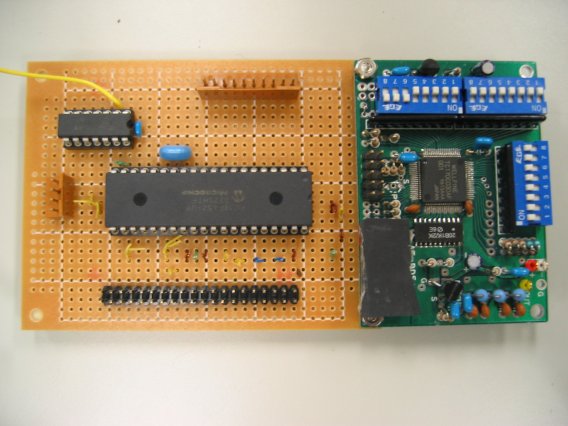

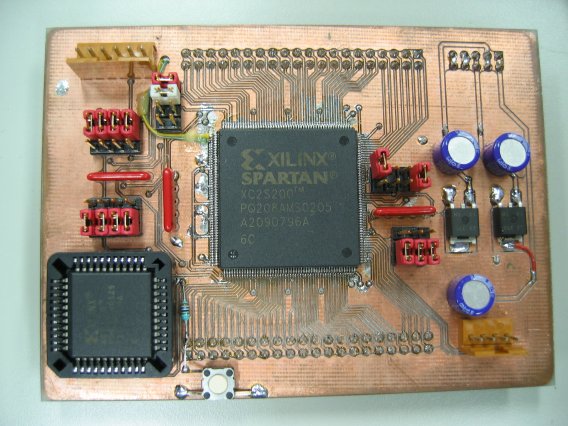

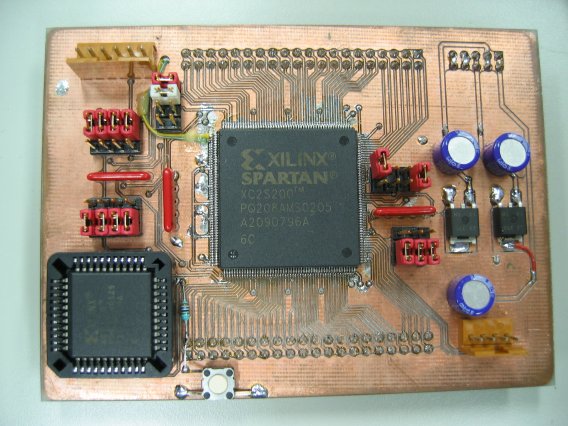

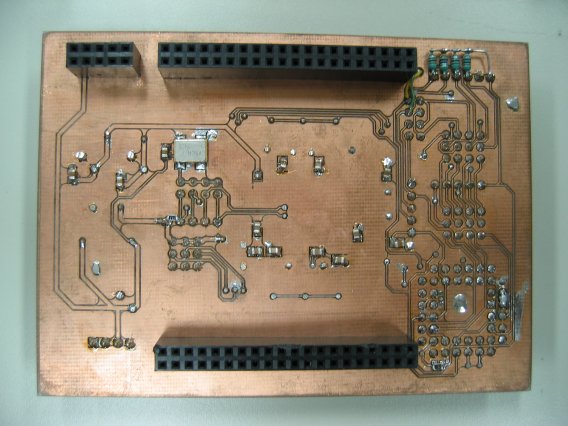

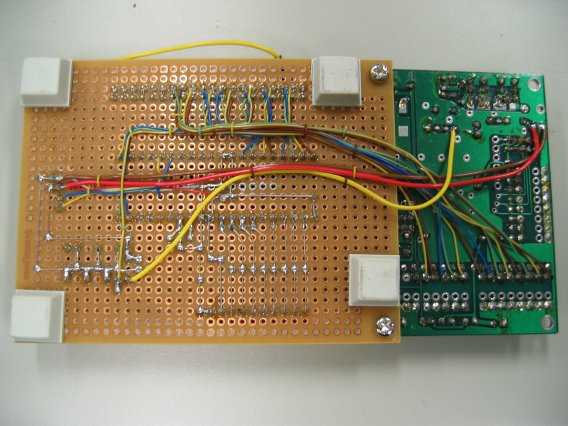

侾丏FPGA偺儃乕僪傪嶌傠偆

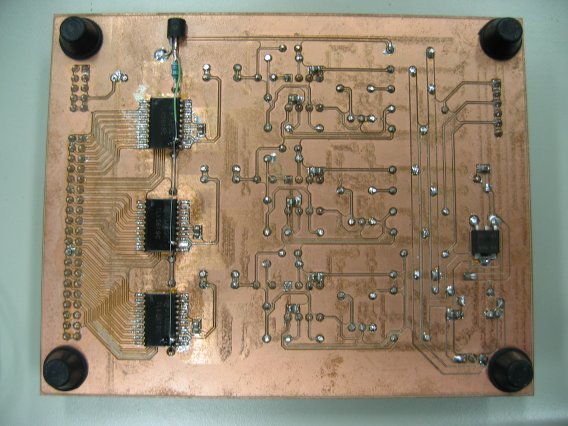

FPGA偲偐偪傚偔偪傚偔巊偭偰偄傠偄傠嶌偭偰偄傞偺偱偡偑丄0.5[mm]僺僢僠偺SOP偺応崌丄僺僢僠曄姺儃乕僪偲偐巊偆偲偳偆偟偰傕僒僀僘偑嫄戝偵側偭偰偟傑偆偺偱偄偮傕偺傛偆偵婎斦壛岺婡偱婎斅傪嶌偭偰偄偒傑偡丅

|

|

偲傝偁偊偢偱偒傑偟偨丅HDL偺儂乕儉儁乕僕乮http://www.hdl.co.jp/home.html乯偵偁傞夞楬恾傪嶲峫偵偟偰嶌傝傑偟偨丅僥僗僩偡傞応崌偱偼丄FPGA偵捈愙JTAG偱偮側偄偱丄僟僂儞儘乕僪偟傑偡丅偁傞掱搙巇忋偑偭偰偒偨傜丄埶棅幰偵搉偡偨傔偵SROM偵彂偒崬傫偱峴偔偲偄偆姶偠偱奐敪傪恑傔偰偄偒傑偡丅

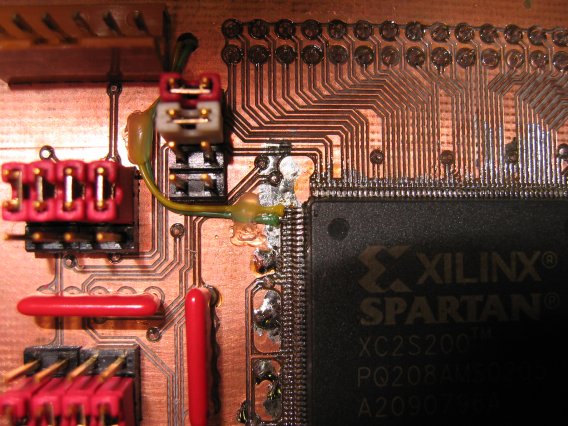

偼偄僶僌傒偭偗丅

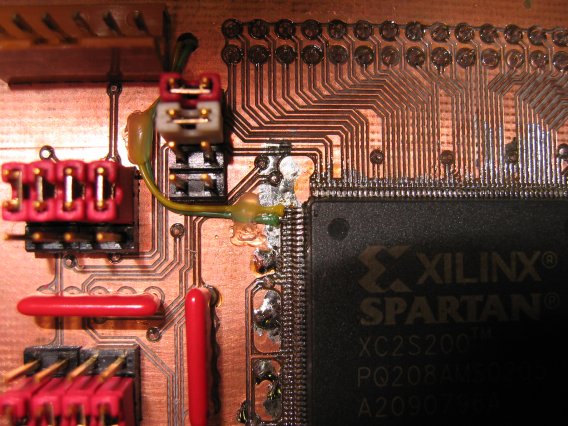

媣乆偵傗偭偰偟傑偄傑偟偨丅俹倰倧倲倕倢偺夞楬恾偺抜奒偱攝慄儈僗丒丒偄偨偄偱偡丅偁乣偁偙傫側偵側偭偰偟傑偭偨丄埲奜偵0.5[mm]偵慄偮偗傞偺偭偰娙扨偱偟偨丅偱傕丄偙偆偄偆偲偙傠偐傜夡傟偰僨僶僢僌偵嬯偟傓傫偩傛側丒丒

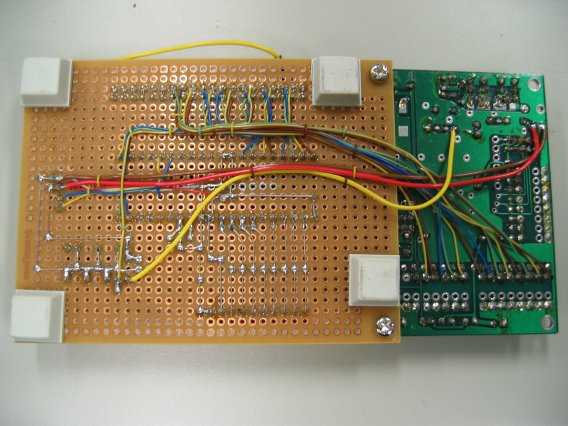

丒婎斅壛岺婡偵傛傞椉柺婎斅偵偮偄偰

婎斅壛岺婡偺椉柺偼僗儖乕儂乕儖偺娭學偱僫乕僶僗偵側傝傑偡丅弶傔偼僒儞僴儎僩偺僗儖僺儞僉僢僩傪巊偭偰偄傑偟偨偑乮http://www.sunhayato.co.jp/catalog/board/board5.html乯婎斅偺嬋偘側偳偵傛傞攳棧乮抐慄乯偑偟傚偭偪傘偆偱偙傟偺僨僶僢僌偵巰偵偦偆偵側偭偨偙偲偑壗搙傕偁傞偺偱丄傕偆巊偄傑偣傫丅偲偔偵丄俬俠僜働僢僩偺懌丄僐僱僋僞側偳偺僗儖乕儂乕儖偺愙怗晄椙偑偐側傝偺妋棪偱偍偙傝傑偡丅偝偭偒傑偱摦偄偰偄偨偺偵丒丒丒偲偄偆働乕僗偑僨僶僢僌偱偼堦斣偨偪埆偄偱偡丅偲偄偆傢偗偱丆偍偡偡傔側偺偑VIA偺宎傪0.8[mm]偵偟偰僪儕儖宎傪0.5[mm]偵偡傞丄偦偟偰0.4[mm]偺庎傔偭偒慄偱昻朢僗儖乕儂乕儖偡傞偺偑堦斣妋幚偱偡丅乮屻攜偺FOX孨偵嫵偊偰傕傜偄傑偟偨乯傑偨丄208PIN偺応崌偼IC偺掙柺偑懌傛傝庒姳崅偄偺偱,FPGA偺壓偵傕昻朢僗儖乕儂乕儖傪嶌傞偙偲偑偱偒傑偡丅偙偺応崌偼偓傝偓傝乮0.2[mm]埵乯傑偱儎僗儕偱敄偔偟偰偍偗偽栤戣側偄偱偡丅婎斅壛岺婡偺応崌偼丄儗僕僗僩偑側偄偺偱僉僢僩偲偐偺婎斅偲斾傋傞偲敿揷偢偗偼偪傚偭偲偩偗擄偟偄偐側丅

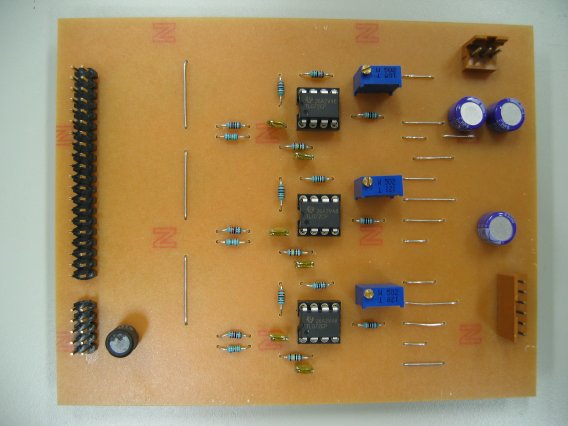

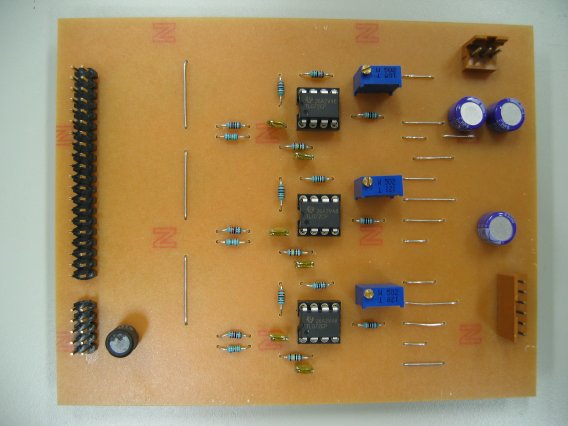

俀丏傾僫儘僌夞楬乮俢乛俙乯偺嶌惉

崱搙偼丄側傫偲偐曅柺偱偄偗偦偆側偺偱妝僠儞偱偡丅婎杮揑偵俁憡暘偺DAC偲僶儞僪僷僗僼傿儖僞乕偩偗偱偡丅庤尦偵偁偭偨DAC偑仜仜偩偭偨偺偱傎傫偲偼12BIT側傫偩偗偳偦傫側偵昁梫側偄傒偨偄偩偭偨偺偱壓埵4BIT巊偭偰偄傑偣傫乮傕偭偨偄側乕乯丅

傑偨僶僌尒偭偗

傑偨僶僌尒偭偗

偙偺DAC側偤偐嵟廔抜偵亊俀攞偺傾儞僾偑擖偭偰偄傞傫偱偡偹乣偲偄偆偙偲偼婎弨揹尮偑俆倁偱偼俵俙倃偱侾侽倁偵側偭偪傖偆偙偲偵側傝傑偡乮幚嵺偵偼DAC偺擖椡揹埑傪挻偊偰偟傑偭偰偄傞偺偱弌偣傑偣傫偑乯丅偁偲丄揹尮偺曄摦偵傕嫮偔偟偨偐偭偨偺偱丄婎弨揹尮梡偺ICLM-??傪巊偆偙偲偵偟傑偟偨丅嬻拞攝慄偱偡乮偲傎傎乯丅傑偨丄僆僼僙僢僩挷惍夞楬傕偮偗傑偟偨偑僶儞僪僷僗僼傿儖僞傪巊偭偰偄傞偺偱丄偼偭偒傝偄偭偰側偔偰傕椙偐偭偨偱偡乮傓偟傠側偄曽偑丒丒丒乯丅

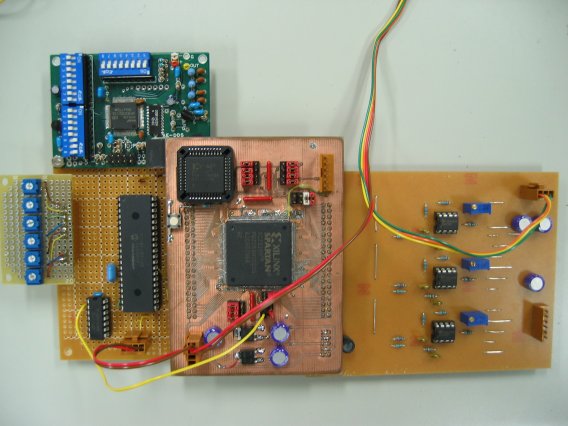

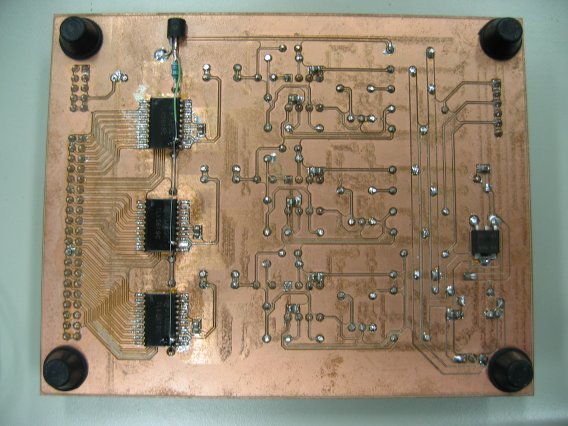

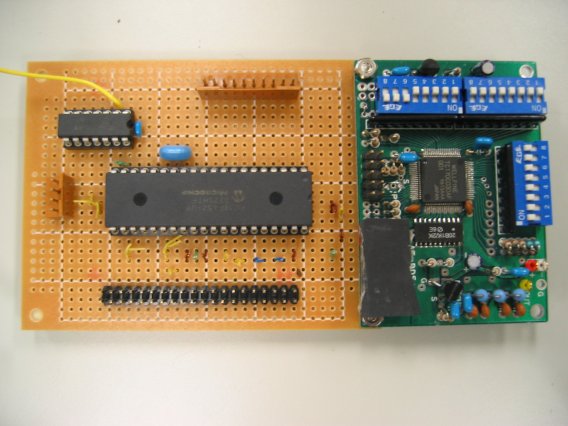

俁丏儅僀僐儞夞楬

巇條側傫偱偡偑PC偺DSP儃乕僪偵偮側偖偗偳傾僫儘僌弌椡偟偐側偄偐傜挷惍偼傾僫儘僌偱丒丒丒偲偄偆側傫偩偐晄巚媍側巇條偵偡傞偨傔偵傑偀傔傫偳偔偝偄偐傜PIC偺AD傪巊偆偙偲偵偟傑偟偨丅夞楬傕庤攝慄偱偡丅偨傇傫墳摎惈擻偼侾侽倠[Hz]掱搙偩偲巚偄傑偡丅偙傟傛傝憗偄偺偑昁梫偵側偭偨傜丄偙偙傪ADC偵偡傟偽偄偄偩偗偱偡偹丅

係丏惂屼僽儘僢僋

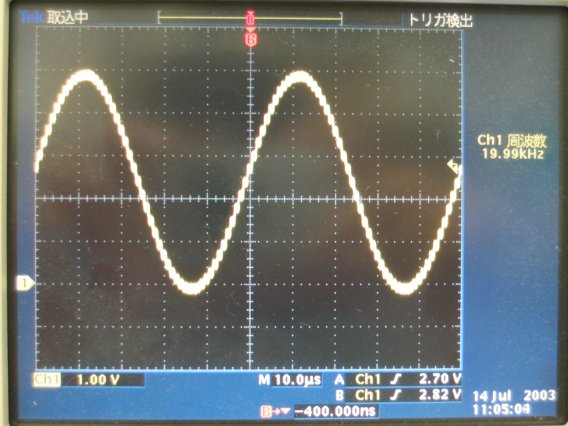

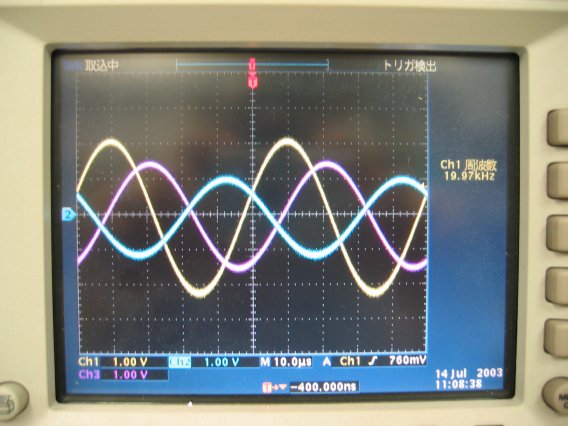

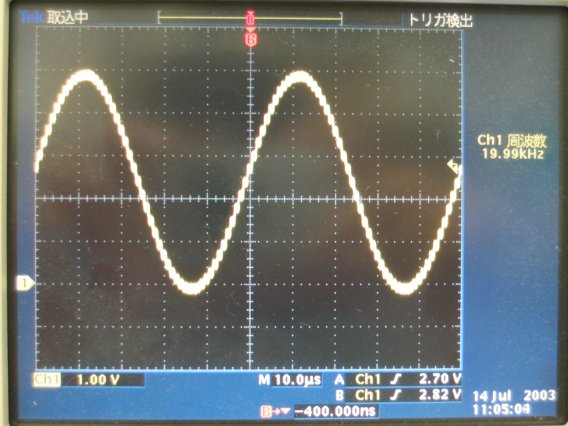

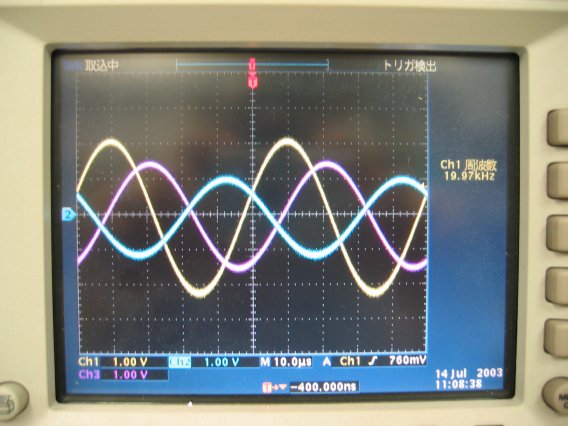

偝偰丄偨偺偟偄僴乕僪偑偱偒偨偐傜師偼桱烼側VHDL偩乕偲偄偆傢偗偱僾儘僌儔儈儞僌嶌嬈偱偡丅婎杮揑偵偼僒僀儞攇偺僥乕僽儖傪嶲徠偟偰DAC偵搉偡偄傢備傞DDS夞楬側傫偱偡偑丄廃攇悢偼20.0k[Hz]乣22.5k[Hz]偱偡丅DAC偼僙僩儕儞僌偑1u[s]偲偄偆偙偲偱20k[Hz]偺僒僀儞攇偩偭偨傜侾廃婜俆侽崗傒乮偮傑傝僒儞僾儕儞僌廃婜侾俵[Hz]乯偺僥乕僽儖偵側傝傑偡丅埵憡傕侾廃婜偱俆侽抜奒偵挷惍偱偒傑偡丅埶棅幰偵偙傟偱偄偄丠偲暦偄偨傜乽廫暘偱偡乿偲偄傢傟偨偺偱崱夞偼偙傟偱峴偒傑偡乮傕偪傠傫僴乕僪愝寁偺慜偵寛傔偰偍偄偨偙偲偱偡偑乯丅怳暆傕侾侽抜奒偖傜偄偁傟偽偄偄偲偄偆偙偲偩偭偨偺偱僥乕僽儖傪侾侽庬椶嶌傞偙偲偱僇僶乕偟傑偟偨丅妱傝嶼偱傕偄偄偲巚偆偗偳偳傟偔傜偄僎乕僩巊偆偐傢偐傫側偐偭偨偺偱偙傟偱偄偒傑偟偨丅廃攇悢偼僥乕僽儖傪揔摉偵娫堷偔傛偆偵偟偰曄偊傜傟傞傛偆偵偟傑偟偨丅

俆丏埶棅幰偐傜婣偭偰偒偰丒丒丒

寢嬊丄廃攇悢偺曄壔傪傕偭偲嵶偐偔偟偰傎偟偄偲偄偆偙偲偩偭偨偺偱丄FPGA偱側傫偲偐偡傟偽偄偄傗偲巚偭偨傫偩偗偳丄儊僀儞偺僋儘僢僋偑20MHz偱僒儞僾儕儞僌廃婜侾俵俫倸偲偡傞偲侾俵俫倸嬤曈偱偼俆侽俲俫倸掱搙偺暘夝擻偟偐傕偰傑偣傫丅傕偆偪傚偭偲暘夝擻傎偟偄側偀偲偄傢傟偙偆側傞偲俹俴俴偲偐巊偆偟偐側偄傫偩偗偳傔傫偳偔偝偐偭偨偺偱丄廐寧偺俢俢俽僉僢僩傪巊偄傑偟偨丅側傫偐弶傔偐傜偙傟巊偊偽傛偐偭偨傛偆側婥偑偟傑偡偑丄暋悢戜偺俢俢俽僉僢僩偵傛傞埵憡嵎偺挷惍偼偦傟偼偦傟偱擄偟偦偆偩偭偨偺偱傑偁偄偄偐丒丒丒丅

偱傕偙偺僉僢僩俢俢俽側偺偵偳偆偟偰侾[Hz]扨埵偱愗傝懼偊傜傟傞偺偩傠偆丒丒偭偲偍傕偭偨傜傗偭傁傝撪晹偵俹俴俴夞楬傪帩偭偰偄傞傛偆偱偟偨乮側偁傫偩乯丅

偱丄傕偆傎傫偲偵傔傫偳偔偝偐偭偨偺偱僨傿僢僾僗僀僢僠偺偲偙傠偐傜捈愙廃攇悢傪偄偠傞偙偲偵偟傑偟偨丅俹俬俠偼侾侽俛倝倲偺俙俢俠傪帩偭偰偄傑偡丅偲偄偆偙偲偼暘夝擻1024偲偄偆偙偲側偺偱偙傟偑20.00k[Hz]乣22.50k[Hz]偺僼儖僗働乕儖偵側傟偽棟憐揑側傢偗偱偡丅

偱丄俢俢俽僉僢僩偲侾侽Bit偱寢傏偆偲巚偭偨傫偱偡偑丄偙偺廃攇悢偭偰偪傚偆偳孞傝忋偑傝偑3BIT傕婲偙偭偰偟傑偆傫偱偡偹丅寢嬊俥俹俧俙偲俢俢俽傪8[Bit]栚偐傜21[Bit]傑偱偺14[Bit]寢慄偟丄俹俬俠偺偐傜偺侾侽俛俬俿偵僆僼僙僢僩傪偐偗偰14[Bit]弌椡偡傞偙偲偱僒儞僾儕儞僌廃攇悢傪917k[Hz]乣1180k[Hz]丄弌椡攇宍廃攇悢傪18.35k[Hz]乣23.59k[Hz]偲偡傞偙偲偑偱偒傑偟偨丅埶棅幰偵偙偺帋嶌傪巊偭偰傕傜偭偰丄偄偄傛偆偱偁傟偽丄侾枃偺婎斅偵偟偰婎斅傗偝傫偵敪拲偡傞偙偲偵側偭偰偄傑偡丅

偱丄俢俢俽僉僢僩偲侾侽Bit偱寢傏偆偲巚偭偨傫偱偡偑丄偙偺廃攇悢偭偰偪傚偆偳孞傝忋偑傝偑3BIT傕婲偙偭偰偟傑偆傫偱偡偹丅寢嬊俥俹俧俙偲俢俢俽傪8[Bit]栚偐傜21[Bit]傑偱偺14[Bit]寢慄偟丄俹俬俠偺偐傜偺侾侽俛俬俿偵僆僼僙僢僩傪偐偗偰14[Bit]弌椡偡傞偙偲偱僒儞僾儕儞僌廃攇悢傪917k[Hz]乣1180k[Hz]丄弌椡攇宍廃攇悢傪18.35k[Hz]乣23.59k[Hz]偲偡傞偙偲偑偱偒傑偟偨丅埶棅幰偵偙偺帋嶌傪巊偭偰傕傜偭偰丄偄偄傛偆偱偁傟偽丄侾枃偺婎斅偵偟偰婎斅傗偝傫偵敪拲偡傞偙偲偵側偭偰偄傑偡丅

傑偨僶僌尒偭偗

傑偨僶僌尒偭偗

偱丄俢俢俽僉僢僩偲侾侽Bit偱寢傏偆偲巚偭偨傫偱偡偑丄偙偺廃攇悢偭偰偪傚偆偳孞傝忋偑傝偑3BIT傕婲偙偭偰偟傑偆傫偱偡偹丅寢嬊俥俹俧俙偲俢俢俽傪8[Bit]栚偐傜21[Bit]傑偱偺14[Bit]寢慄偟丄俹俬俠偺偐傜偺侾侽俛俬俿偵僆僼僙僢僩傪偐偗偰14[Bit]弌椡偡傞偙偲偱僒儞僾儕儞僌廃攇悢傪917k[Hz]乣1180k[Hz]丄弌椡攇宍廃攇悢傪18.35k[Hz]乣23.59k[Hz]偲偡傞偙偲偑偱偒傑偟偨丅埶棅幰偵偙偺帋嶌傪巊偭偰傕傜偭偰丄偄偄傛偆偱偁傟偽丄侾枃偺婎斅偵偟偰婎斅傗偝傫偵敪拲偡傞偙偲偵側偭偰偄傑偡丅

偱丄俢俢俽僉僢僩偲侾侽Bit偱寢傏偆偲巚偭偨傫偱偡偑丄偙偺廃攇悢偭偰偪傚偆偳孞傝忋偑傝偑3BIT傕婲偙偭偰偟傑偆傫偱偡偹丅寢嬊俥俹俧俙偲俢俢俽傪8[Bit]栚偐傜21[Bit]傑偱偺14[Bit]寢慄偟丄俹俬俠偺偐傜偺侾侽俛俬俿偵僆僼僙僢僩傪偐偗偰14[Bit]弌椡偡傞偙偲偱僒儞僾儕儞僌廃攇悢傪917k[Hz]乣1180k[Hz]丄弌椡攇宍廃攇悢傪18.35k[Hz]乣23.59k[Hz]偲偡傞偙偲偑偱偒傑偟偨丅埶棅幰偵偙偺帋嶌傪巊偭偰傕傜偭偰丄偄偄傛偆偱偁傟偽丄侾枃偺婎斅偵偟偰婎斅傗偝傫偵敪拲偡傞偙偲偵側偭偰偄傑偡丅